## GT74LVC595 8-Bit Shift Registers with 3-State Output Registers

| 1 Features                                                                                                                                                                                                                                                                                                                                                                                      | 2 Application                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Wide Operating Voltage Range: 1.65V to 5.5V</li> <li>Inputs Accept Voltages Higher than the Supply Voltage</li> <li>All Inputs with Schmitt-Trigger Actions</li> <li>Shift register has direct clear</li> <li>Balanced Propagation Delays</li> <li>Operation Temperature Range</li> <li>-40°C to +125°C, TA</li> <li>Available in Green TSSOP16 and SOP16</li> <li>Packages</li> </ul> | <ul> <li>Output expansion</li> <li>LED matrix control</li> <li>7-segment display control</li> <li>8-bit data storage</li> </ul> |

#### 3 Description

The GT74LVC595 device contains an 8-bit, serialin,parallel-out shift register that feeds an 8-bit D-type storage register. The storage register has parallel 3-state outputs.Separate clocks are provided for both the shift and storage register.Both the shift register and storage register have separate clocks. The shift register clock (SRCLK) is positive-edge triggered. Data is shifted on the positive-going transitions of the SRCLK. The storage register clock (RCLK) is also positive-edge triggered. The data in each register is transferred to the storage register on a positive-going transition of the RCLK.The shift register has a direct overriding clear (SRCLR) input, serial (SER) input, and a serial output (Q<sub>H'</sub>) for cascading.When the output-enable (OE) input is high, the storage register outputs are in a highimpedance state. Internal register data and serial output  $(Q_{H'})$  are not impacted by the operation of the  $\overline{OE}$  input.

## **4 Revision History**

| Revision   | Date         | Note                            |

|------------|--------------|---------------------------------|

| Rev. A1. 0 | 2024. 04. 07 | Original version                |

| Rev. A1. 1 | 2024. 12. 13 | Updated Marking and Package Qty |

The latest datasheet version should be checked on the GTIC official website, as the company does not actively inform customers about updates to the datasheet.

### **5 Device Summary, Pin and Packages**

Table 5-1. Device Summary<sup>(1)</sup>

| Serial Name | Part Name    | Package | Body Size (Nom)      | Marking <sup>(2)</sup> | MSL <sup>(3)</sup> | Package Qty           |

|-------------|--------------|---------|----------------------|------------------------|--------------------|-----------------------|

| GT74LVC595  | GT74LVC595TE | TSSOP16 | 5.00mm×4.40mm×0.90mm | GT74LVC595<br>XXXXXXX  | 3                  | Tape and<br>Reel,4000 |

| GT74LVC595  | GT74LVC595PE | SOP16   | 9.9mm×3.9mm×1.40mm   | GT74LVC595<br>XXXXXXX  | 3                  | Tape and<br>Reel,4000 |

(1)For all available packages, please contact product sales.

(2)There may be additional marking, which relates to the lot trace code information (data code and Vendor code), the logo or the environmental category on the device.

(3)MSL, The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications.

(4)"XXXXX" in Marking will be appeared as the batch code.

## 5 Device Summary, Pin and Packages(Continued)

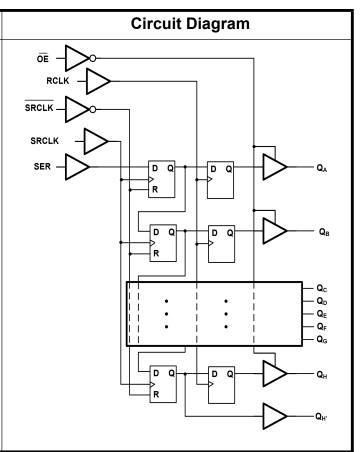

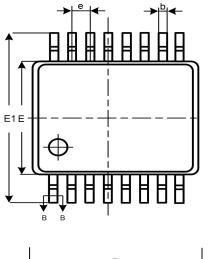

### Fig.5-1 GT74LVC595: TE(TSSOP16) Package

GT74LVC595: PE(SOP16) Package

| Table 5-1 Pin Definition |

|--------------------------|

|--------------------------|

| PIN              | l   | I/O | DESCRIPTION                                 |

|------------------|-----|-----|---------------------------------------------|

| NAME             | NO. | 1/0 | DESCRIPTION                                 |

| Q <sub>B</sub>   | 1   | 0   | Q <sub>B</sub> Output                       |

| Qc               | 2   | 0   | Q <sub>C</sub> Output                       |

| QD               | 3   | 0   | Q <sub>D</sub> Output                       |

| QE               | 4   | 0   | Q <sub>E</sub> Output                       |

| QF               | 5   | 0   | Q <sub>F</sub> Output                       |

| Q <sub>G</sub>   | 6   | 0   | Q <sub>G</sub> Output                       |

| Q <sub>H</sub>   | 7   | 0   | Q <sub>H</sub> Output                       |

| GND              | 8   | -   | Ground                                      |

| Q <sub>H</sub> ' | 9   | 0   | Serial O, can be used for cascading         |

| SRCLR            | 10  | I   | Shift register clear, active low            |

| SRCLK            | 11  | I   | Shift register clock, rising edge triggered |

| RCLK             | 12  | I   | O register clock, rising edge triggered     |

| ŌĒ               | 13  | I   | O Enable, active low                        |

| SER              | 14  | I   | Serial Input                                |

| Q <sub>A</sub>   | 15  | 0   | Q <sub>A</sub> Output                       |

| VCC              | 16  | -   | Positive supply                             |

\*It is suggested to leave the unconnected pins floating.

## 6 Voltage, Temperature, ESD and Thermal Ratings

#### 6.1 Absolute Maximum Ratings

|                  | Parameter                           | S                                                                             | Min | Max. | Unit |

|------------------|-------------------------------------|-------------------------------------------------------------------------------|-----|------|------|

| Vcc              | Supply volt                         | Supply voltage range                                                          |     |      |      |

| Іік              | Input clamp current <sup>(1)</sup>  | Input clamp current <sup>(1)</sup> V <sub>I</sub> < -0.5V                     |     |      | mA   |

| I <sub>ОК</sub>  | Output clamp current <sup>(2)</sup> | $Output clamp current^{(2)} V_{O} < -0.5V \text{ or } V_{O} > V_{CC} + 0.5 V$ |     |      | mA   |

| VI               | Input voltage                       |                                                                               |     | 7    | V    |

| lo               | Output current                      |                                                                               |     | 25   | mA   |

| lcc              | Continuous current t                | hrough V <sub>CC</sub> or GND                                                 | -75 | 75   | mA   |

| TJ               | Junction temperature under bias     |                                                                               |     | 150  | °C   |

| T <sub>stg</sub> | Storage temperature range           |                                                                               | -65 | 150  | °C   |

| Soldering        | Lead Tem                            | nperature                                                                     |     | 260  | °C   |

(1)Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute maximum ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional. Operating the device in this manner may affect device reliability, functionality, performance, and shorten the device lifetime.

(2)The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

#### 6.2 ESD Ratings

|        |                                | Value                                                 | Unit  |   |

|--------|--------------------------------|-------------------------------------------------------|-------|---|

|        | V(ESD) Electrostatic discharge | Human-Body Model (HBM)                                | ±3.5K | V |

| V(ESD) |                                | D) Electrostatic discharge Charged Device Model (CDM) | ±2K   | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6 Voltage, Temperature, ESD and Thermal Ratings(Continued)

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted).

| SYMBOL   | PARAMI                              | MIN                 | MAX | UNIT |      |

|----------|-------------------------------------|---------------------|-----|------|------|

| Vcc      | Supply V                            | 1.65                | 5.5 | V    |      |

| VI       | Input vo                            | 0                   | 5.5 | V    |      |

| Vo       | Output vo                           | Output voltage      |     |      | V    |

| <u> </u> |                                     | VCC=3 V to 3.6V     |     | 100  | ns/V |

| Δt/ΔV    | Input transition rise and fall rate | VCC=4.5 V to 5.5V   |     | 20   | ns/V |

| TA       | Ambient tem                         | Ambient temperature |     |      | °C   |

#### 6.4 Thermal Information

| Package Type | θ <sub>JA</sub> | θյς | Unit |

|--------------|-----------------|-----|------|

| SOP16        | 73              |     | °C/W |

| TSSOP16      | 108             |     | °C/W |

### **7 Electrical Specifications**

### 7.1 Electrical Characteristics

Full=-40°C to +125°C, Typical values are at TEMP=+25°C. (unless otherwise noted)

|                           |                 |                                                                     | Υ.                                                    | ,                                         |                      |                                                   |                 |                                   |                                          |      |  |

|---------------------------|-----------------|---------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------|----------------------|---------------------------------------------------|-----------------|-----------------------------------|------------------------------------------|------|--|

| PARAMETER                 | SYMBOL          |                                                                     | CONDITIONS                                            | TEMP                                      | MIN                  | TYP                                               | MAX             | UNITS                             |                                          |      |  |

|                           |                 | V <sub>CC</sub> =2V                                                 |                                                       | Full                                      | 1.5                  |                                                   |                 |                                   |                                          |      |  |

| High-level Input Voltage  | VIH             |                                                                     | V <sub>CC</sub> =3V                                   | Full                                      | 2.1                  |                                                   |                 | v                                 |                                          |      |  |

|                           |                 |                                                                     | V <sub>CC</sub> =5.5V                                 | Full                                      | 3.85                 |                                                   |                 |                                   |                                          |      |  |

|                           |                 |                                                                     | Vcc=2V                                                | Full                                      |                      |                                                   | 0.5             |                                   |                                          |      |  |

| Low-level Input Voltage   | VIL             |                                                                     | V <sub>CC</sub> =3V                                   | Full                                      |                      |                                                   | 0.9             | v                                 |                                          |      |  |

|                           |                 |                                                                     | V <sub>CC</sub> =5.5V                                 | Full                                      |                      |                                                   | 1.65            |                                   |                                          |      |  |

|                           |                 |                                                                     | $V_{CC}$ =2V to 4.5V,I <sub>O</sub> =-50 uA           | Full                                      | V <sub>cc</sub> -0.1 |                                                   |                 |                                   |                                          |      |  |

| High-level Output Voltage | V <sub>он</sub> | V <sub>OH</sub>                                                     | $V_{I}\!\!=\!\!V_{IH} \text{ or } V_{IL}$             | V <sub>cc</sub> =3V,I <sub>o</sub> =-4 mA | Full                 | 2.5                                               |                 |                                   | v                                        |      |  |

|                           |                 |                                                                     | V <sub>CC</sub> =4.5V,I <sub>0</sub> =-8 mA           | Full                                      | 3.8                  |                                                   |                 |                                   |                                          |      |  |

|                           | V <sub>OL</sub> | V <sub>OL</sub>                                                     | V <sub>OL</sub>                                       | V <sub>OL</sub>                           |                      | V <sub>cc</sub> =2V to 4.5V,I <sub>o</sub> =50 uA | Full            |                                   |                                          | 0.1  |  |

| Low-level Output Voltage  |                 |                                                                     |                                                       |                                           | V <sub>OL</sub>      | V <sub>OL</sub>                                   | V <sub>OL</sub> | $V_I = V_{IH} \text{ or } V_{IL}$ | V <sub>CC</sub> =3V,I <sub>O</sub> =4 mA | Full |  |

|                           |                 |                                                                     | Vcc=4.5V,Io=8 mA                                      | Full                                      |                      |                                                   | 0.5             |                                   |                                          |      |  |

| Input Lookage Current     |                 |                                                                     |                                                       | <b>+25</b> ℃                              |                      | ±0.1                                              | ±0.5            |                                   |                                          |      |  |

| Input Leakage Current     | lı              | Vcc                                                                 | =0V to 5.5V,V <sub>I</sub> =5.5V or GND               | FULL                                      |                      |                                                   | ±1              | μA                                |                                          |      |  |

| Off state Outsut Oursent  |                 | <u> </u>                                                            |                                                       | <b>+25</b> ℃                              |                      | ±0.1                                              | ±0.5            |                                   |                                          |      |  |

| Off-state Output Current  | loz             | VI= VIH                                                             | or $V_{IL}$ , $V_0$ = $V_{CC}$ or GND, $V_{CC}$ =5.5V | FULL                                      |                      |                                                   | ±1              | μA                                |                                          |      |  |

| Supply Current            |                 |                                                                     | -5 5)///-)/ or CND 104                                | <b>+25</b> ℃                              |                      | 0.1                                               | 1               |                                   |                                          |      |  |

| Supply Current            | lcc             | $V_{CC}$ =5.5V,V <sub>I</sub> = $V_{CC}$ or GND, I <sub>0</sub> =0A |                                                       | FULL                                      |                      | 5                                                 | 5               | μA                                |                                          |      |  |

| Input Capacitance         | Ci              |                                                                     |                                                       | <b>+25℃</b>                               |                      | 6                                                 |                 | pF                                |                                          |      |  |

## 7 Electrical Specifications (Continued)

### 7.2 Switching Characteristics

over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                                  | SYMBOL           |                                        | -CONDITIONS                   |         | TEMP | MIN <sup>(1)</sup> | TYP  | MAX <sup>(1)</sup> | UNITS |

|--------------------------------------------|------------------|----------------------------------------|-------------------------------|---------|------|--------------------|------|--------------------|-------|

|                                            |                  |                                        |                               | C∟=15pF | Full |                    |      |                    |       |

|                                            |                  |                                        | V <sub>CC</sub> =3V to 3.6V   | C∟=50pF | Full |                    | 10   | 15                 | ns    |

|                                            |                  | SRCLK to Q <sub>H</sub> <sup>(2)</sup> |                               | C∟=15pF | Full |                    |      |                    |       |

|                                            |                  |                                        | $V_{CC}$ =4.5V to 5.5V        | C∟=50pF | Full |                    | 8    | 10                 | ns    |

|                                            |                  |                                        |                               | C∟=15pF | Full |                    |      |                    |       |

| Propagation Delay                          |                  |                                        | $V_{CC}$ =3V to 3.6V          | C∟=50pF | Full |                    | 10.5 | 15                 | ns    |

| FTOPagation Delay                          | t <sub>pd</sub>  | RCLK to Qn <sup>(2)</sup>              |                               | C∟=15pF | Full |                    |      |                    |       |

|                                            |                  |                                        | $V_{CC}$ =4.5V to 5.5V        | C∟=50pF | Full |                    | 8    | 12                 | ns    |

|                                            |                  |                                        |                               | C∟=15pF | Full |                    |      |                    |       |

|                                            |                  |                                        | $V_{CC}$ =3V to 3.6V          | C∟=50pF | Full |                    | 8    | 15                 | ns    |

|                                            |                  | SRCLR to Q <sub>H</sub> <sup>(3)</sup> |                               | C∟=15pF | Full |                    |      |                    |       |

|                                            |                  |                                        | $V_{CC}$ =4.5V to 5.5V        | C∟=50pF | Full |                    | 6    | 10                 | ns    |

| Enable Time <sup>(4)</sup> t <sub>en</sub> |                  | OE to Qn                               | V <sub>cc</sub> =3V to 3.6V   | C∟=15pF | Full |                    |      |                    | ns    |

|                                            |                  |                                        |                               | C∟=50pF | Full |                    | 8    | 12                 |       |

|                                            | t <sub>en</sub>  |                                        | $V_{cc}$ =4.5V to 5.5V        | C∟=15pF | Full |                    |      |                    | - ns  |

|                                            |                  |                                        |                               | C∟=50pF | Full |                    | 7    | 10                 |       |

|                                            |                  | OE to Qn                               | )/)/+= 2 ()/                  | C∟=15pF | Full |                    |      |                    |       |

|                                            |                  |                                        | $V_{CC}$ =3V to 3.6V          | C∟=50pF | Full |                    | 8    | 11                 | ns    |

| Disable Time <sup>(5)</sup>                | t <sub>dis</sub> |                                        |                               | C∟=15pF | Full |                    |      |                    |       |

|                                            |                  |                                        | $V_{CC}$ =4.5V to 5.5V        | C∟=50pF | Full |                    | 7    | 10                 | ns    |

|                                            |                  |                                        | V <sub>CC</sub> =3V to 3      | 3.6V    | Full |                    |      |                    |       |

| Maximum Frequency                          | f <sub>MAX</sub> | SRCLK or RCLK                          | V <sub>CC</sub> =4.5V to      | 5.5V    | Full |                    | 130  |                    | MHz   |

|                                            |                  |                                        | V <sub>CC</sub> =3V to 3      | 3.6V    | Full | 5                  |      |                    |       |

|                                            |                  | SRCLK high or low                      | Vcc=4.5V to 5.5V              |         | Full | 5                  |      |                    | ns    |

| Pulse Duration                             |                  |                                        | V <sub>CC</sub> =3V to 3      | 3.6V    | Full | 5                  |      |                    |       |

| Fuise Duration                             | tw               | RCLK high or low                       | V <sub>CC</sub> =4.5V to      | 5.5V    | Full | 5                  |      |                    | ns    |

|                                            |                  |                                        | V <sub>CC</sub> =3V to 3      | 3.6V    | Full | 5                  |      |                    |       |

|                                            |                  | SRCLR low                              | V <sub>cc</sub> =4.5V to 5.5V |         | Full | 5                  |      |                    | ns    |

|                                            |                  |                                        | V <sub>cc</sub> =3V to 3      | 3.6V    | Full | 3                  |      |                    |       |

| Octore T                                   |                  | SER to SRCLK                           | V <sub>CC</sub> =4.5V to      | 5.5V    | Full | 3                  |      |                    | ns    |

| Setup Time                                 | t <sub>su</sub>  |                                        | V <sub>cc</sub> =3V to 3      | 3.6V    | Full | 5                  |      |                    |       |

|                                            |                  | SRCLK to RCLK                          | V <sub>CC</sub> =4.5V to      | 5.5V    | Full | 5                  |      |                    | ns    |

# 7 Electrical Specifications (Continued)

| PARAMETER                                          | SYMBOL           |                                    | CONDITIONS                  |              |     | TYP | MAX <sup>(1)</sup> | UNITS |

|----------------------------------------------------|------------------|------------------------------------|-----------------------------|--------------|-----|-----|--------------------|-------|

| Hold Time th                                       |                  | SER to SRCLK                       | V <sub>CC</sub> =3V to 3.6V | Full         | 2.5 |     |                    | - ns  |

|                                                    | ι'n              |                                    | $V_{CC}$ =4.5V to 5.5V      | Full         | 2   |     |                    |       |

| Dessurer                                           |                  | t <sub>REC</sub> SRCLR to SRCLK    | V <sub>CC</sub> =3V to 3.6V | Full         | 3   |     |                    | ns    |

| Recovery Time                                      | L <sub>REC</sub> |                                    | $V_{CC}$ =4.5V to 5.5V      | Full         | 3   |     |                    |       |

| Power Dissipation<br>Capacitance <sup>(6)(7)</sup> | C <sub>PD</sub>  | $f_i=1$ MHz, $V_i=GND$ to $V_{CC}$ |                             | <b>+25</b> ℃ |     | 30  | 60                 | pF    |

NOTES:

1.Specified by design and characterization; not production tested.

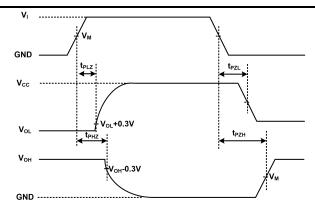

2.  $t_{\text{PD}}$  is the same as  $t_{\text{PHL}}$  and  $t_{\text{PLH}}.$

3.  $t_{\text{PD}}$  is the same as  $t_{\text{PHL}}$  only.

4.  $t_{\text{EN}}$  is the same as  $t_{\text{PZL}}$  and  $t_{\text{PZH}}.$

5.  $t_{\text{DIS}}\,\text{is the same as }t_{\text{PLZ}}\,\text{and}\,\,t_{\text{PHZ.}}$

$6.C_{\text{PD}}$  is used to determine the dynamic power dissipation (P\_D in uW).

$P_{D}=C_{PD}\times V_{CC}^{2}\times f_{I}+\sum (C_{L}\times V_{CC}^{2}\times f_{o}).$

where:

$f_i$  = Input frequency in MHz.

f<sub>o</sub>= Output frequency in MHz.

$C_L$ = Output load capacitance in pF.

V<sub>CC</sub> = Supply voltage in Volts.

$\Sigma(C_L \times Vcc^2 \times f_0)$ = Sum of outputs.

7. All 9 outputs switching.

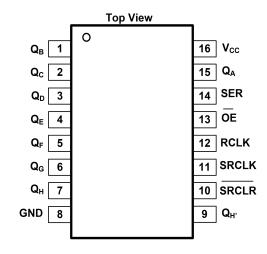

## 8 Typical Characteristics

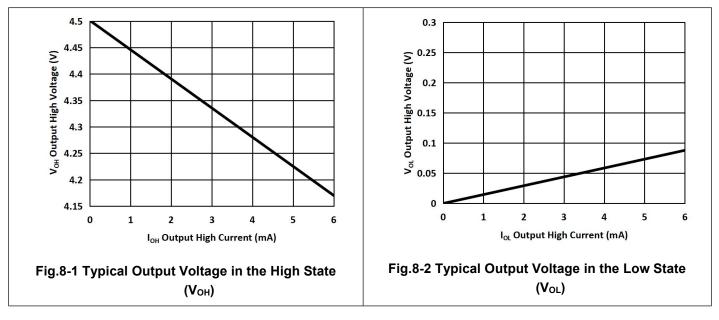

### **9** Parameter Measurement Information

Fig.9-1 Test Circuit for Measuring Switching Times

Test conditions are given in Table 9-1.

Definitions test circuit:

RL: Load resistance.

CL: Load capacitance (includes jig and probe).

$R_T$ : Termination resistance (equals to output impedance  $Z_o$  of the pulse generator)

S<sub>1</sub>: Test selection switch.

#### Tabel 9-1 Test Condition

| Supply Voltage | Input                            |        | Lo        | ad | S1 Position                                                           |     |                                    |  |

|----------------|----------------------------------|--------|-----------|----|-----------------------------------------------------------------------|-----|------------------------------------|--|

| Vcc            | VI t <sub>R</sub> t <sub>F</sub> |        | CL        | R∟ | t <sub>PHL</sub> ,t <sub>PLH</sub> t <sub>PZH</sub> ,t <sub>PHZ</sub> |     | t <sub>PZL</sub> ,t <sub>PLZ</sub> |  |

| 1.65V to 5.5V  | Vcc                              | ≤3.0ns | 15pF,50pF | 1k | Open                                                                  | GND | Vcc                                |  |

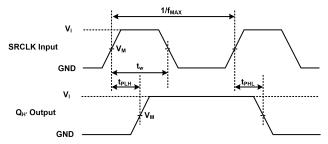

Fig.9-2 Shift Clock Pulse, Maximum Frequency and Input to Output Propagation Delays

Test conditions are given in Table 9-1.

Measurement points are given in Table 9-2.

Logic levels:  $V_{\text{OL}}$  and  $V_{\text{OH}}$  are typical output voltage levels that occur with the output load

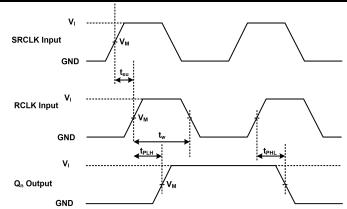

Fig.9-3 Storage Clock to Output Propagation Delays

Test conditions are given in Table 9-1.

Measurement points are given in Table 9-2.

Logic levels:  $V_{\text{OL}}$  and  $V_{\text{OH}}$  are typical output voltage levels that occur with the output load.

Fig.9-4 Data Set-Up and Hold Times

Test conditions are given in Table 9-1.

Measurement points are given in Table 9-2.

Logic levels:  $V_{OL}$  and  $V_{OH}$  are typical output voltage levels that occur with the output load.

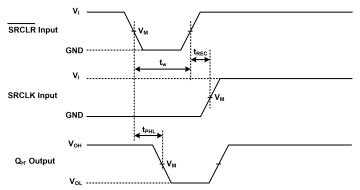

Fig.9-5 Master Reset to Output Propagation Delays

Test conditions are given in Table 9-1. Measurement points are given in Table 9-2.

Logic levels:  $V_{OL}$  and  $V_{OH}$  are typical output voltage levels that occur with the output load.

Fig.9-6 Enable and Disable Times

Test conditions are given in Table 9-1.

Measurement points are given in Table 9-2.

Logic levels:  $V_{\text{OL}}$  and  $V_{\text{OH}}$  are typical output voltage levels that occur with the output load.

| Tabel 9-2 | Measurement Points |

|-----------|--------------------|

|-----------|--------------------|

| Supply Voltage  | Input                         | Output              |  |  |

|-----------------|-------------------------------|---------------------|--|--|

| V <sub>cc</sub> | V <sub>M</sub> <sup>(1)</sup> | V <sub>M</sub>      |  |  |

| 1.65V to 5.5V   | 0.5×V <sub>CC</sub>           | 0.5×V <sub>CC</sub> |  |  |

NOTE.

1. The measurement points should be Vim or V'i when the input rising or falling time exceeds 3.0ns.

### **10 Detailed Description**

#### 10.1 Balanced CMOS 3-State Outputs

This device includes balanced CMOS 3-State outputs. The three states that these outputs can be in are driving high, driving low, and high impedance. The term balanced indicates that the device can sink and source similar currents. The drive capability of this device may create fast edges into light loads so routing and load conditions should be considered to prevent ringing. Additionally, the outputs of this device are capable of driving larger currents than the device can sustain without being damaged. It is important for the output power of the device to be limited to avoid damage due to over current. The electrical and thermal limits defined in the Absolute Maximum Ratings must be followed at all times.

For the high-impedance state, the output voltage is not controlled by the device and is dependent on external factors. If no other drivers are connected to the node, then this is known as a floating node and the voltage is unknown. A pull-up or pull-down resistor can be connected to the output to provide a known voltage at the output while it is in the high-impedance state. The value of the resistor will depend on multiple factors, including parasitic capacitance and power consumption limitations. Typically, a 10 k $\Omega$  resistor can be used to meet these requirements.

#### 10.2 Balanced CMOS Push-Pull Outputs

This device includes balanced CMOS push-pull outputs. The term balanced indicates that the device can sink and source similar currents. The drive capability of this device may create fast edges into light loads so routing and load conditions should be considered to prevent ringing. Additionally, the outputs of this device are capable of driving larger currents than the device can sustain without being damaged. It is important for the output power of the device to be limited to avoid damage due to over current. The electrical and thermal limits defined in the Absolute Maximum Ratings must be followed at all times.

|     | Table 10-1 Function Table |        |      |    |                                                                                                                 |  |  |  |  |

|-----|---------------------------|--------|------|----|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     |                           | INPUTS |      |    |                                                                                                                 |  |  |  |  |

| SER | SRCLK                     | SRCLR  | RCLK | ŌĒ | FUNCTION                                                                                                        |  |  |  |  |

| x   | x                         | x      | х    | н  | Outputs $Q_A - Q_H$ are disabled                                                                                |  |  |  |  |

| x   | x                         | х      | х    | L  | Outputs $Q_A - Q_H$ are enabled                                                                                 |  |  |  |  |

| х   | х                         | L      | Х    | х  | Shift register is cleared                                                                                       |  |  |  |  |

| L   | Ţ                         | Н      | х    | х  | First stage of the shift register goes low.<br>Other stages store the data of previous stage,<br>respectively.  |  |  |  |  |

| Н   | 1                         | Н      | х    | х  | First stage of the shift register goes high.<br>Other stages store the data of previous stage,<br>respectively. |  |  |  |  |

| х   | х                         | Н      | ↑ _  | х  | Shift-register data is stored in the storage register                                                           |  |  |  |  |

| x   | ↑                         | Н      | ¢    | х  | Data in shift register is stored in the storage register, the data is then shifted through.                     |  |  |  |  |

#### **10.3 Device Functional Modes**

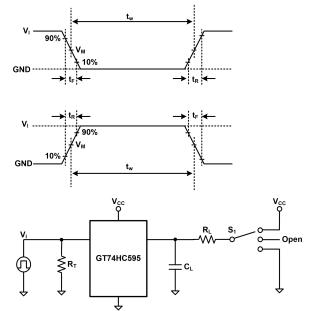

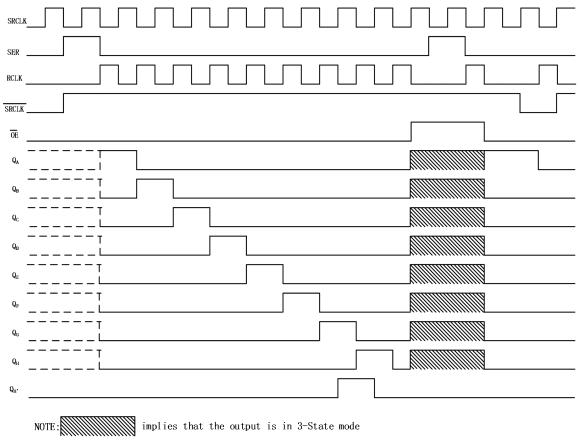

Fig.10-1 Timing Diagram

### **11 Application Information**

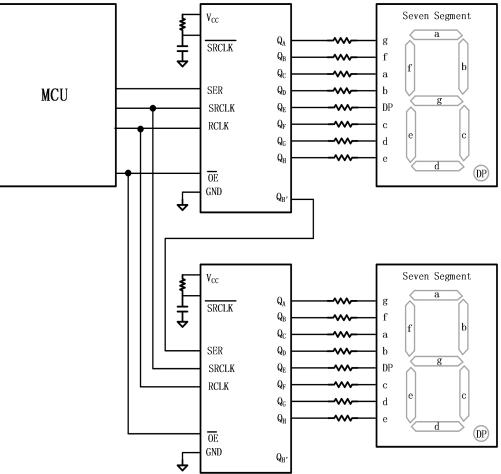

In this application, the GT74LVC595 is used to control seven-segment displays. Utilizing the serial output and combining a few of the input signals, this implementation reduces the number of I/O pins required to control the displays from sixteen to four. Unlike other I/O, the GT74LVC595 does not need a communication interface for control. It can be easily operated with simple GPIO pins.

The OE pin is used to easily disable the outputs when the displays need to be turned off or connected to a PWM signal to control brightness. However, this pin can be tied low and the outputs of the GT74LVC595 can be controlled accordingly to turn off all the outputs reducing the I/O needed to three. There is no practical limitation to how many GT74LVC595 devices can be cascaded. To add more, the serial output will need to be connected to the following serial input and the clocks will need to be connected accordingly. With separate control for the shift registers and output registers, the desired digit can be displayed while the data for the next digit is loaded into the shift register. At power-up, the initial state of the shift registers and output registers are unknown. To give them a defined state, the shift register needs to be cleared and then clocked into the output register.

**Fig.11-1 Typical Application Schematic**

## 12 Package Outline Dimension

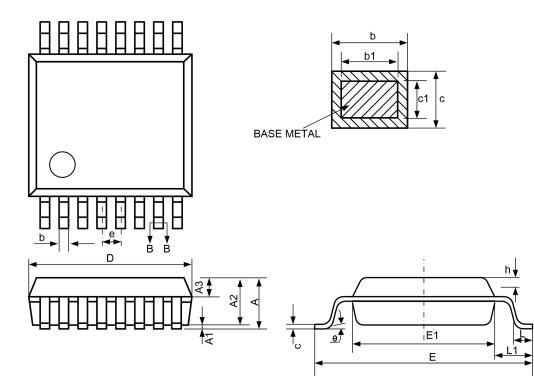

### TSSOP16

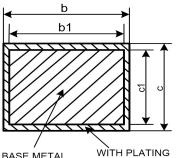

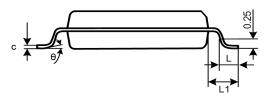

BASE METAL WITH PLATI SECTION B-B

| Symbol | Din     | nensions In I | Millimeters | Dimensions In Inches |       |       |  |  |

|--------|---------|---------------|-------------|----------------------|-------|-------|--|--|

| Symbol | Min     | Nom           | Мах         | Min                  | Nom   | Мах   |  |  |

| A      |         |               | 1.20        |                      |       | 0.047 |  |  |

| A1     | 0.05    |               | 0.15        | 0.002                |       | 0.006 |  |  |

| A2     | 0.80    | 1.00          | 1.05        | 0.031                | 0.039 | 0.041 |  |  |

| A3     | 0.39    | 0.44          | 0.49        | 0.015                | 0.017 | 0.019 |  |  |

| b      | 0.19    |               | 0.30        | 0.007                |       | 0.012 |  |  |

| b1     | 0.19    | 0.22          | 0.25        | 0.007                | 0.009 | 0.010 |  |  |

| С      | 0.13    |               | 0.18        | 0.005                |       | 0.007 |  |  |

| c1     | 0.12    | 0.13          | 0.14        | 0.005                | 0.005 | 0.006 |  |  |

| D      | 4.86    | 4.98          | 5.10        | 0.191                | 0.196 | 0.201 |  |  |

| E      | 4.30    | 4.40          | 4.50        | 0.169                | 0.173 | 0.177 |  |  |

| E1     | 6.20    | 6.40          | 6.60        | 0.244                | 0.252 | 0.260 |  |  |

| е      | 0.65BSC |               |             | 0.026BSC             |       |       |  |  |

| L      | 0.45    | 0.60          | 0.75        | 0.018                | 0.024 | 0.030 |  |  |

| L1     | 1.00BSC |               |             | 0.039BSC             |       |       |  |  |

| θ      | 0°      |               | 8°          | 0°                   |       | 8°    |  |  |

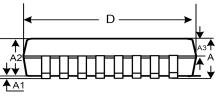

# 12 Package Outline Dimension(Continued)

SOP16

| symbol | Dime | nsions In Millime | eters | Dimensions In Inches |       |       |  |  |

|--------|------|-------------------|-------|----------------------|-------|-------|--|--|

| Symbol | Min  | Nom               | Max   | Min                  | Nom   | Max   |  |  |

| A      |      |                   | 1.75  |                      |       | 0.069 |  |  |

| A1     | 0.10 |                   | 0.225 | 0.004                |       | 0.009 |  |  |

| A2     | 1.30 | 1.40              | 1.50  | 0.051                | 0.055 | 0.059 |  |  |

| b      | 0.39 |                   | 0.47  | 0.015                |       | 0.019 |  |  |

| b1     | 0.38 | 0.41              | 0.44  | 0.015                | 0.016 | 0.017 |  |  |

| С      | 0.20 |                   | 0.24  | 0.008                |       | 0.009 |  |  |

| c1     | 0.19 | 0.20              | 0.21  | 0.007                | 0.008 | 0.008 |  |  |

| D      | 9.80 | 9.90              | 10.00 | 0.386                | 0.390 | 0.394 |  |  |

| E      | 5.80 | 6.00              | 6.20  | 0.228                | 0.236 | 0.244 |  |  |

| E1     | 3.80 | 3.90              | 4.00  | 0.150                | 0.154 | 0.157 |  |  |

| е      |      | 1.27(BSC)         |       | 0.05(BSC)            |       |       |  |  |

| h      | 0.25 |                   | 0.50  | 0.010                |       | 0.020 |  |  |

| L      | 0.50 |                   | 0.80  | 0.020                |       | 0.031 |  |  |

| L1     |      | 1.05REF           |       | 0.041REF             |       |       |  |  |

| θ      | 0°   |                   | 8°    | 0°                   |       | 8°    |  |  |

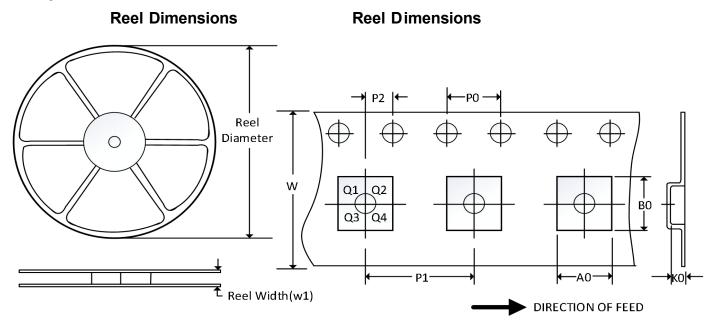

### 13 Tape and Reel Information

Note: The picture is only for reference. Please make the object as the standard.

#### Key Parameter List of Tape and Reel

| Package Type | Reel<br>Diameter | Reel Width<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TSSOP16      | 13"              | 12.4               | 6.90       | 5.60       | 1.20       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

| SOP16        | 13"              | 16.4               | 6.60       | 9.30       | 2.10       | 4.0        | 8.0        | 2.0        | 16.0      | Q1               |

Note:

(1)All dimensions are nominal.

(2)Plastic or metal protrusions of 0.15mm maximum per side are not included.